1 引言

在航天飞行器研制初期,遥测系统负责各类参数的

数据采集和

存储工作,可获得飞行器飞行过程中环境参数、重要控制数据以及图像数据,为飞行器性能评估和改进提供重要数据支持。而存储器作为遥测系统的重要组成部分,可以记录完整的全程数据,通过硬回收的方式获取试验数据,相比于无线遥测受限于带宽和传输距离的影响,存储器可以提供更为准确和详细的试验数据,为后续改进提供依据。传统遥测系统只是需要记录某些环境参数及一些控制数

据,对数据量和传输速率要求不高,一般容量为4GB, 传输速率为20MB/s即可满足要求,但随着飞行器对性能和准确度的要求,系统和产品不断增加,需要记录的数据也越来越多,尤其是导引头技术的发展,数据量提高了3~4 倍,传输速率也高达数Gbps,传统的存储器无法满足需求,同时由于速率的增加,落地环境更加恶劣,存储器的可靠回收也成为一个大挑战。

本文针对上述问题,提出了高速低误码高可靠回收存储器的设计方法,将存储容量提高到 128G字节,速率可达2.4Gbps,并通过交叉冗余备份方式,实现了存储器的高可靠回收。

2 总体设计方案

2.1 硬件设计方案

根据系统需求,为了满足高冲击环境下可靠回收的要求,存储器的设计原则是在满足性能的情况下尽量减小体积和重量,通过灌封的方式保护存储芯片,提高存储器的抗冲击能力。存储器设计的关键是选择存储芯片。目前市场上应用最多的大容量存储芯片主要有UFS、eMMC 及NAND Flash三类。UFS全称是Universal Flash Storage,即“通用闪存存储”,采用串行数据传输技术,有两个数据通道,工作模式为全双工;eMMC全称为 embedded Multi Media Card, 即“嵌入式多

媒体存储卡”,采用并行数据传输技术,拥有8位数据线,工作模式为半双工。该两种产品依托于操作系统实现复杂的接口协议,广泛应用于手机存储领域。但在航天领域高强度、高可靠性及恶劣回收环境的应用场合,NAND Flash应用广泛,其接口操作简单,在不使用操作系统的情况下就满足系统要求。经过调研,结合开发经验,最终选择美国Micron公司的NAND Flash 芯片,该芯片单片容量可达16GB,读写速率可达50MB/s,且该芯片封装为表贴SOP形式,拆卸方便,能够在最坏的情况下通过拆卸芯片的方式实现回收。

在选定存储芯片后,考虑到高速数据传输需求以及小型化要求,选择Altera的MAX10 FPGA,该芯片不需要外置配置芯片,减小了体积。同时该芯片支持高速LVDS接口,可以通过内部的IP来实现。

电路来接收地面或其他设备传送过来的控制指令,包括擦除、记录、下载等,该设计中使用双路光耦进行接收,起到冗余备份的作用。数据下载通过普通LVDS进行,为了减小体积,使用FPGA内部自带的LVDS接口来模拟LVDS编码器发送数据,发送数据时使用8b10b编码,然后通过 LVDS 驱动芯片发送给接口设备,完成数据的下载和状态的汇报。综上所述,最终确定了存储器的硬件设计方案。存储器由3块板卡组成,分别为一块FPGA控制板和2块Flash阵列板(一块存储数据,一块备份数据),其中FPGA控制板完成对2块Flash阵列板的读写控制以及与接口设备的通信,包括命令控制、数据的输入以及数据下载等;2 块Flash 阵列板相同,通过柔性板和FPGA控制板连接,每个FPGA阵列板上具有数据回读接口,在落地后FPGA板卡损害严重的情况下可以通过该接口将数据找回。

图1:存储器设计原理框图

如图1所示,接口设备需要配合存储器一起工作来完成所有功能。接口设备将通过其他接口和外系统进行通信并接收总速率高达200MB/s的数据,然后将各路数据进行统一编帧整合成一路数据通过SoftLVDS接口发送给存储器。为了满足长距离可靠传输要求,设计时采用一路时钟和四路数据的方式来传输数据,每路数据带宽为600Mbps,共同实现2.4Gbps的数据传输。存储器接收到数据后通过SoftLVDS接口缓存到变位宽FIFO中,32bit进64bit出,然后

将64bit数据同时存放到NAND Flash中,共需要8片NAND Flash芯片,每片速度30MB/s,小于芯片最大50M/s的能力,此方案可行,能够满足系统需求。

2.2 软件设计方案

根据系统要求和硬件设计方案,通过设计FPGA软件实现功能。设计时将FPGA软件划分为以下7个功能模块:时钟产生模块、复位信号产生模块、顶层控制模块、数据接收缓存模块、指令接收模块、FLASH控制模块以及数据输出控制模块。各模块相互关系如图2所示。

图2:FPGA软件各模块相互关系

2.2.1 时钟产生模块

该模块用于产生系统全局时钟和各个模块运行所需时钟信号。共需要2个PLL(锁相环)模块:一个PLL是利用晶振输入时钟产生系统所需要的各种时钟。另外一个PLL用来同步高速LVDS数据。为了保证随路时钟能够正确采样到数据,对随路时钟进行相移操作。此设计中PLL的输入为60M随路时钟,输出为相移144°后的同频时钟输出给数据接收模块。

2.2.2 复位信号产生模块

该模块用于产生全局复位信号。通过PLL锁相环的LOCK信号和计数器共同产生一个大于400ms的全局复位信号,用于复位全部模块和变量。

2.2.3 顶层控制模块

该模块用于控制本软件的运行状态,包顶层控制模块提供配置使能信号使配置模块开始对各模块进行配置。配置完成后,顶层控制模块使用原理图的形式,控制本软件进入运行状态,开始进行指令和数据的接收,并执行响应的操作。

2.2.4 数据接收缓存模块

数据接收缓存模块接口形式为高速LVDS接口,包括4路LVDS数据和一路LVDS时钟。存储器对接收到的LVDS信号进行解析,将有效数据放入FIFO中。

2.2.5 指令接收控制模块

指令接收控制模块用于接收RS422指令,并对指令进行解析,从而产生其他模块所需要的使能信号。

2.2.6 Flash控制模块

该模块是FPGA软件的核心部分,主要根据指令完成对Flash的操作。该存储器共有16片 Flash,分成两组P1和P2,P1和P2互为备份,功能相同。根据Micron芯片手册设计以下7个子模块:复位模块、配置模块、读 ID模块、上电检测模块、擦除模块、写模块和读模块。各子模块处理流程如图3所示。

图3:Flash控制模块处理流程

(1)复位模块。根据芯片手册要求,Flash正常工作首先需要一个复位操作,复位操作后才能进行后续模块。为了保证可靠性,设计时如果复位不成功,则进行重试,重试次数为10次,若10次不成功反馈错误结果。

(2)配置模块。配置模块对Flash芯片的工作模式进行设定,根据需要设定相应的工作模块。上电默认为Timemode0, 该设计中将工作模式设定在Timemode4。采用和复位模块一样的可靠性设计方法,若配置不成功,重试10次。

(3)读ID模块。该模块为了检查16个Flash 上电是否正常工作,将检查结果反馈给地面测试系统。该模块的另一个重要功能是在回收后,上电检查16个芯片的正常与否,快速定位到损坏芯片,使用与之冗余备份的芯片读取数据。

(4)上电监测模块。根据手册,NAND Flash在出厂时允许有一定的坏块量,所以在进行擦除、读、写操作之前需要将Flash坏块检测出来。Flash的坏块标记位置在每个块第一页的第8192位置,标记为0x00。为了提高Flash的写入速度,设计时采用双面操作,两个片选信号(CE)乒乓操作。为了保证块地址整体移动,设计时将两个CE的双面地址共4个块地址一起进行判断,若其中有一个坏块则跳过该块。检查坏块时建立一个1bit×4096的RAM表,坏块标记为‘0’,好块标记为‘1’。通过该RAM表,可以在擦除、记录和下载时进行查询,确保操作正常块区域,保证数据的正确存储。

(5)擦除模块。Flash擦除操作为Flash写操作的前提。擦除时,首先需要根据上电检测模块建立的坏块 RAM表进行判断,坏块不进行擦除操作;若好块在擦除过程中不成功,则需要将其标记为坏块,即在该快的第一页的8192地址处标记为0x00,同时更新坏块RAM表。

(6)写模块。该模块用于对Flash进行编程存储。设计时采用双面操作增加写入速度,双面操作减少了等待Flash每页编程的时间,可以保证数据快速连续的写入到存储单元中。在写入过程中为降低误码率,增加ECC纠错编码算法,将计算出的ECC编码存放到每一页的用户区域中,供后读数据时比较和判断。

(7)读模块。读模块用于将Flash中数据读出,同样由于使用了双面操作,读出数据时也需要进行双面操作。读出数据的同时计算ECC编码值,并和写入时的原ECC编码进行比较,若有不同则计算出bit反转位置并纠正过来。

通过上述软件设计,实现了高速低误码高可靠回收存储器设计,经过试验考核,性能稳定。

3 关键技术及解决途径

3.1 基于SoftLVDS的高速数据传输

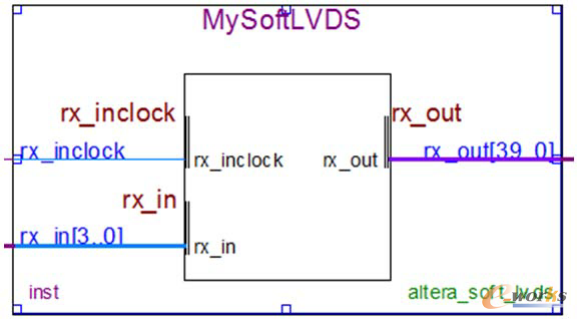

本设计中使用到了Altera自带的高速LVDS接口IP核,通过例化该IP,并根据硬件设计配置相应的参数,可快速实现两个设备间的高速数据传输。QuartusII中Altera SoftLVDS IP核如图4所示。

图4:Altera SoftLVDS IP核例化图

如图4所示,该IP核只有两个输入信号和一个输出信号,输入信号中的rx_inclock为上文讲到的接收到的随路时钟经过倍频后的时钟,随路时钟为60MHz,经过5倍频输出为300MHz,SoftLVDS IP内部采用双边沿采样对四路数据进行采杨实现600Mbps的传输,每一路数据恢复出10bit并行数据,四路共恢复成40路并行数据,其中高8位为控制信号,到为0xC0时表示后面32bit数据为有效数据,在随路时钟即60MHz相移144°后的时钟采样下缓存到FIFO中,从而完成数据的正确传输。

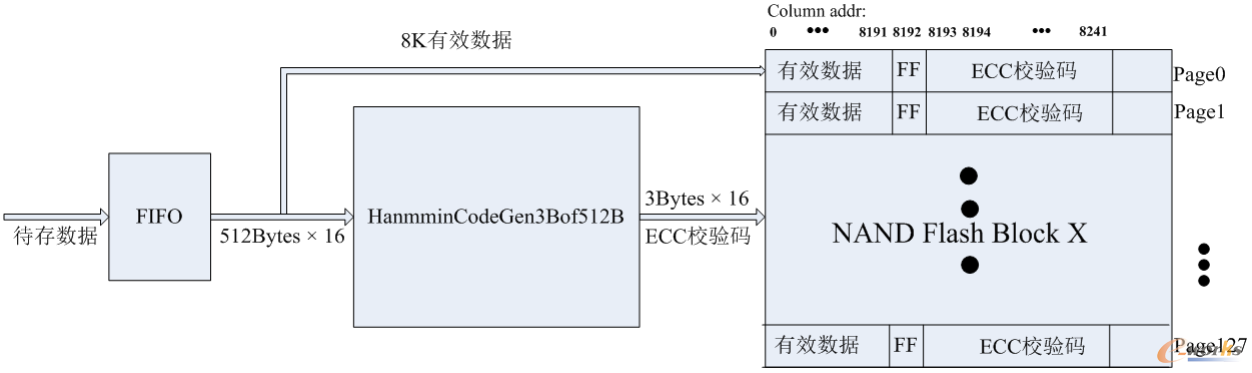

3.2 基于ECC的NAND Flash控制技术

由于硬件所选的NAND Flash的容量为16GB,由数据块和数据页组成,读写操作均以页为单位进行,一页为 8KB和448B字节的用户空闲空间组成。由于设计时使用ECC算法每512个字节产生3字节检验码,因此在NAND Flash的每页的用户空闲区需要存储48字节的校验码。当数据从FIFO中取出写入NAND Flash时,需要根据原始数据使用“HanmminCodeGen3Bof512B”产生ECC校验码,其产生原理框图如图5所示。

图5:ECC校验码产生框图

按照图5所示的步骤,产生48字节的检验码存放在每页地址从8193开始的用户空闲区。当需要从NAND Flash中读取数据时,需要使用“HanmminCodeGen3Bof512B”模块重新生成48B字节的校验码同时将8K数据存放在RAM中等待进行纠正。新ECC校验码和原ECC检验码在“ErrLocation”模块中进行比较,找到位翻转位置,然后进入“RdCtrl_withECC”模块对8K待纠正数据的对应位置的数据位进行纠正,纠正完后将数据输出,其处理流程图如图6所示。

图6:ECC进行位翻转纠正处理框图

经过上述两个步骤,即实现了ECC算法, 将该部分实现代码加入到整个NAND Flash的控制器中,实现了bit纠错,将误码率降低到10-10以下。

3.3 交叉冗余备份设计

存储器需要适应高速冲击环境,设计的重点就是要保护Flash芯片的安全。在硬件设计上,将两个Flash阵列板通过柔性版一上一下折叠放入圆柱形结构中进行灌封处理。每个Flash阵列板中的8个Flash芯片正反面放置,每面4个。通过炮击试验发现,相同位置的Flash芯片容易同时受到损坏。为了尽量避免该情况发生,设计时将备份Flash阵列板上的Flash芯片进行交叉冗余备份,真正起到备份的目的。在某个芯片损坏的情况下,通过备份的芯片可以恢复出数据。存储器安装后两组Flash的相对位置示意图如图7所示。

图7:两组Flash的相对位置示意图

如图7所示,Flash芯片D1~D8和D9-D16分别存放数据的data[0]~data[63]位。为降低该风险,设计时将P1的数据存放位置不变,P2的数据存放位置D9-D16改为data[63]~data[0], 通过交换管脚的方式实现。更改后的数据存放位置与P1中的数据位置关系如图8所示。

图 8:软件调整后的Flash中数据存放位置示意图

经过调整后,相同位置的Flash存储数据不同,存放相同数据的两片Flash分别位于存储器板的不同位置,回收时若一个阵列中有某个Flash芯片损坏,另一个阵列中存放该位置的芯片没有损坏,则可以通过更改FPGA引脚的方式重新组合成一个完整的存储阵列,将数据读出,从而降低了回收的风险,提高回收的可靠性。

4 结束语

本文针对航天飞行器对存储器高速率、大容量、低误码率以及高冲击环境下可靠回收的要求,设计了一款存储器,该存储器使用SoftLVDS高速传输技术、基于ECC的NAND Flash控制技术以及交叉冗余备份技术实现了高达2.4Gbps传输速率、128G大容量以及小于10-10的设计目标,满足了系统需求,通过了试验验证,可靠回收数据。

参考文献

[1] 李智中,金文, 王小珲.基于1553B总线的再入遥测系统[J].遥测遥控,2018,1:53-56.

[2] 孙琦,苗岩松.基于Flash存储介质的遥测系统高速存储技术研究[J]. 无线电工程 ,2018,48(2):111-115.

[3]胡世明,康怀祺,腾云龙.高速大容量存储系统的应用设计[J].火控雷达技术 ,2012,41(1):34-41.

[4] 张耀,徐智勇,张启衡等.小型化高速数据记录器[J].仪表技术与

传感器 ,2011,4:63-65.

[5] 甄国涌,单彦虎.弹载固态记录器高速存储体系结构设计[J].计算机工程,2013,39(3):275-278.

[6] 朱知博.基于NAND Flash的高速大容量存储系统设计[J].现代电子技术,2011,34(8):170-173.

[7] 陈明义,连帅军,周建国.基于FPGA的Flash控制器系统设计及实现[J].电子科技 ,2008(7):11-13.

作者简介

王伟伟 (1986-),男,河北省衡水市人。硕士研究生,工程师,从事嵌入式设计方向工作。

徐进(1985-),硕士研究生,高级工程师。研究方向为数字信号处理。

李京锋(1978-),大学本科学历,技师。研究方向为硬件电路测试。

李骥(1978-),硕士研究生,研究员。研究方向为电子技术与通信工程。

修展(1987-),硕士研究生,工程师。研究方向为嵌入式设计。

本文来源于互联网,e-works本着传播知识、有益学习和研究的目的进行的转载,为网友免费提供,并已尽力标明作者与出处,如有著作权人或出版方提出异议,本站将立即删除。如果您对文章转载有任何疑问请告之我们,以便我们及时纠正。联系方式:editor@e-works.net.cn tel:027-87592219/20/21。